# L-C-Band Low-Voltage BiCMOS MMIC's for Dual-Mode Cellular-LAN Applications

Mohammad Madhian, *Senior Member, IEEE*, Kiyotaka Imai, Hiroshi Yoshida, Yasushi Kinoshita, and Tohru Yamazaki

**Abstract**— This paper is concerned with the design considerations and performance results for low-voltage Si monolithic microwave/millimeter-wave integrated circuits (MMIC's) developed for mobile and personal communications applications. A  $0.4\text{ }\mu\text{m}$  ECL-BiCMOS process technology was employed to develop bipolar-based RF amplifiers, MOS-based IF amplifiers, BiCMOS-based simplified Gilbert mixers, and monolithic down-converter as well as upconverter IC's incorporating these elements. These converters are designed to operate at a bias voltage of 2 V over 1.8–6.2 GHz exhibiting a conversion gain of 35–15 dB with a variable IF frequency of up to several 100 MHz. Chip size for both the downconverter and upconverter IC's is 1.0 mm  $\times$  0.7 mm.

## I. INTRODUCTION

RECENT advances in cellular phone and wireless network technologies, including 1.9 GHz PCS and DECT, 2.4 GHz ISM band WAN, and 5.2 GHz Hiperlan [1] have urged development of low-cost, small-size, low-power fully monolithic RF/IF modules covering the above frequency bands. Presently available modules operate with 3–6 V dc voltage and can offer a maximum bit rate of 2 Mbps [2]–[4]. There are also some attempts recently reported to achieve RF modules operating with 1.9–2.7 V dc voltage [5]–[7]. However, all these modules can operate over a frequency range of 1.5–2.5 GHz with an IF frequency of up to 100 MHz. To facilitate high-speed transmission of voice, data, and video in such a personal wireless system, and to enable development of a dual-mode PCMCIA card for cellular—LAN system application, achievement of low-power 2 V-class downconverter/upconverter modules covering the full frequency range of 1.9–5.2 GHz with IF frequencies in the several MHz to several 100 MHz range is indispensable.

The present paper combines high frequency potential features of bipolar transistors with low power characteristics of MOS devices in an optimized circuit design, to realize downconverter and upconverter chips operating at 2 V and covering the 1.8–6.2 GHz frequency range with a variable IF frequency of up to several 100 MHz.

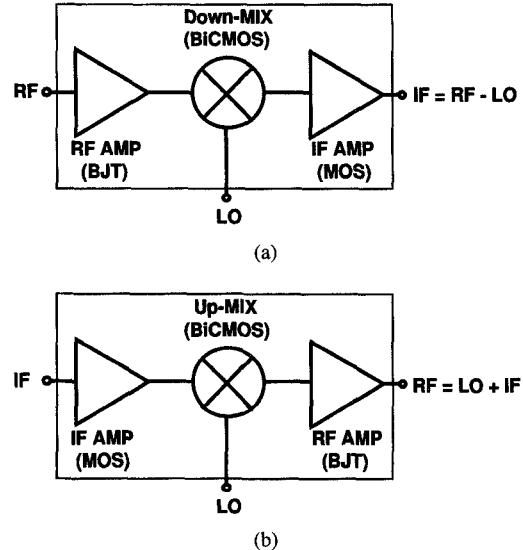

Fig. 1. Block diagrams of (a) downconverter and (b) upconverter.

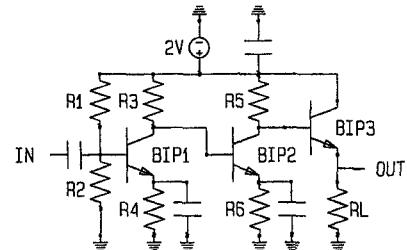

Fig. 2. Equivalent circuit for RF amplifier.

Fig. 3. Equivalent circuit for IF amplifier.

## II. CIRCUIT DESIGN

Block diagrams for the downconverter and upconverter modules are shown in Fig. 1. Each module consists of an RF amplifier, an IF amplifier, and a mixer. Applying several SPICE simulations, we adopted an optimum selection of

Manuscript received July 26, 1995; revised July 22, 1996.

M. Madhian is with Network Research Laboratory, C&C Research Laboratories, NEC Corporation, 4-1-1, Miyazaki, Miyamae-ku, Kawasaki 216 Japan.

K. Imai, H. Yoshida, Y. Kinoshita, and T. Yamazaki are with ULSI Device Development Laboratories, NEC Corporation, 1120, Shimokuzawa, Sagamihara 229 Japan.

Publisher Item Identifier S 0018-9480(96)07917-3.

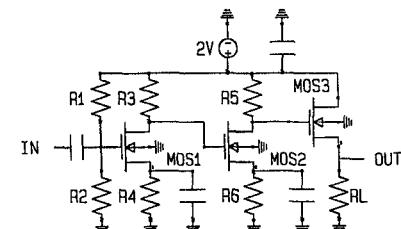

Fig. 4. Equivalent circuits for (a) downconverter's mixer and (b) upconverter's mixer.

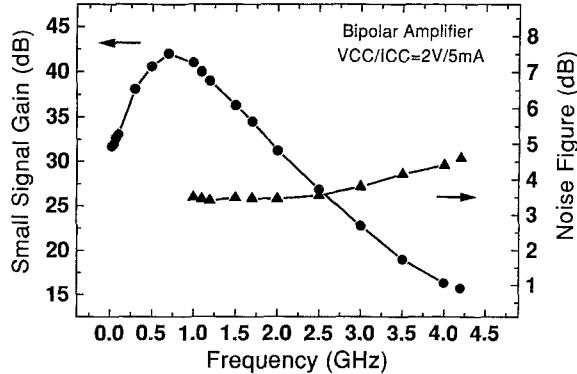

Fig. 5. Small signal gain and noise figure for RF amplifier.

bipolar and MOS technologies for different stages in the RF and IF amplifiers, as well as the mixer, for:

- 1) achieving the highest conversion gain at a nominal supply voltage of 2 V;

- 2) obtaining a wide RF bandwidth covering 1.8–6.2 GHz, and a wide IF bandwidth covering up to 1000 MHz; and

- 3) suppressing the local oscillator (LO) and other unnecessary signals, without employing a particular filtering circuit which otherwise increases the chip size. Moreover, a high impedance interstage matching design approach

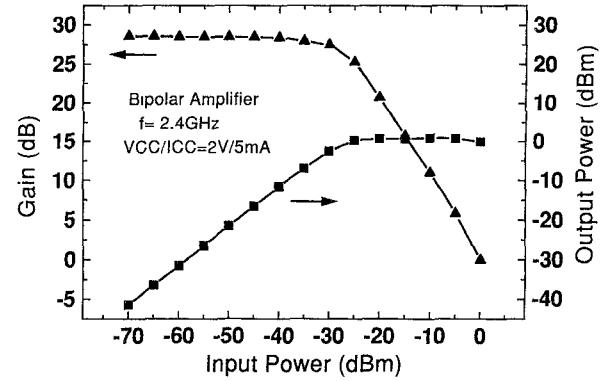

Fig. 6. Input-output power characteristics for RF amplifier.

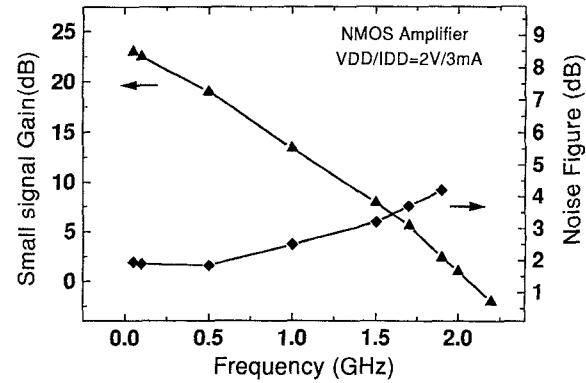

Fig. 7. Small signal gain and noise figure for IF amplifier.

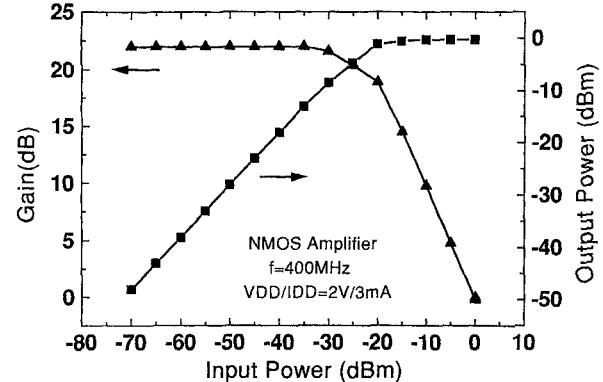

Fig. 8. Input-output power characteristics for IF amplifier.

was applied for keeping the power consumption low, and avoiding conversion gain degradation.

#### A. RF Amplifier

An equivalent circuit for the RF amplifier is shown in Fig. 2. To enhance a high frequency operation for the downconverter and the upconverter, a bipolar-based circuit topology was adopted for the RF amplifier. The amplifier has a simple 2-stage common emitter configuration followed by an emitter follower buffer stage. The emitter area for bipolar transistors BIP1 and BIP2 in the common emitter stages is  $0.8 \mu\text{m} \times 6.4 \mu\text{m}$ , while the emitter size for transistor BIP3 in the buffer stage is twice that for the common emitter stage to increase the amplifier output level.

Fig. 9. Mixers' performance versus input power level.

(a)

(b)

Fig. 11. (a) Downconverter and (b) upconverter performance versus input power.

(a)

(b)

Fig. 10. Chip photographs for (a) downconverter and (b) upconverter.

### B. IF Amplifier

An equivalent circuit for the IF amplifier is shown in Fig. 3. The IF amplifier resembles the RF amplifier but utilizes NMOS transistors which require less dc power and can provide sufficient gain for the IF signal frequency range. The IF amplifier is also responsible for attenuating high frequency components at the amplifier's output port, through optimization of an RC-filter realized by parallel combination of bias resistors R1 and R2, and the gate-source capacitance of the first common source

transistor MOS1. Gate length and width for transistors MOS1 and MOS2 in the common source stages are, respectively,  $0.4 \mu\text{m}$  and  $50 \mu\text{m}$ . Gate width for transistor MOS3 in the buffer stage is twice that for the common source to enhance output power.

### C. Mixers

Equivalent circuits for the mixers used in each frequency converter are presented in Fig. 4. To assure a 2 V dc power operation and low LO power requirement, a simplified Gilbert cell was adopted, and voltage drop distribution for load resistors R3, R4, series-gated transistors B1 to B6, and current source transistors MOS1, MOS2 in the cell was optimized based on a SPICE simulation. Use is made of bipolar transistors in the cell which is responsible for a high frequency mixing of the LO and RF signals. A current source circuit for each mixer employs NMOS transistors for their low power requirement and applicability as a power control device. To realize a 2 V operation, voltage drops for the NMOS, each bipolar transistor in the series-gated cell, and the load resistor are 0.7, 0.5, and 0.3 V, respectively, under a condition that reference voltages VB1 and VB2 are adjusted to provide a collector current equal to 4 mA. The mixer in the downconverter module utilizes an NMOS push-pull buffer stage, while the mixer in the upconverter module uses a bipolar emitter

(a)

(b)

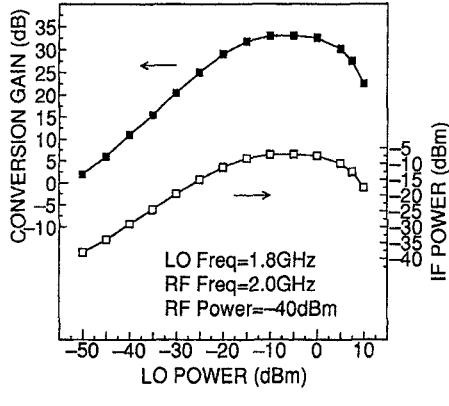

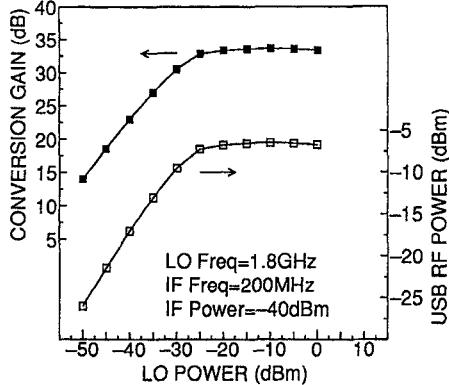

Fig. 12. (a) Downconverter and (b) upconverter performance versus LO power.

follower buffer stage. Emitter area for a bipolar transistor in the mixers is  $0.8 \mu\text{m} \times 6.4 \mu\text{m}$ , and gate area for an NMOS is  $0.4 \mu\text{m} \times 50 \mu\text{m}$ .

#### D. Filtering

The present downconverter and upconverter modules make use of no particular on-chip or off-chip filter for suppressing unnecessary signals at the output port. As it was stated earlier, high frequency filtering characteristics of NMOS push-pull buffer stage in the downconverter module's mixer and an optimized RC-filtering feature of the NMOS IF amplifier are utilized to realize excellent isolation characteristics for each module.

### III. FABRICATION PROCESS AND DEVICE CHARACTERISTICS

The chips were fabricated employing a  $0.4 \mu\text{m}$  ECL-BiCMOS process technology which has been developed for high speed digital circuit applications [8]. The bipolar transistor has a double polysilicon self-aligned emitter-base structure, and an NMOS transistor has a WSi/polysilicon gate LDD structure. To fabricate the load and bias resistors, polysilicon layers with different sheet resistances were used, and to fabricate bypass and dc blocking capacitances, a poly-to-poly structure was employed. A  $0.8 \mu\text{m} \times 6.4 \mu\text{m}$  bipolar transistor has a typical  $\beta$  and  $f_T$  of, respectively, 40

(a)

(b)

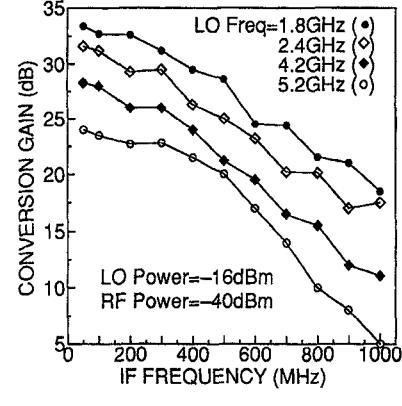

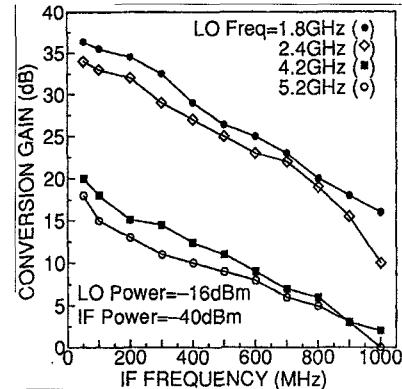

Fig. 13. (a) Downconverter and (b) upconverter performance versus IF frequency with LO frequency as a parameter.

and 20 GHz at a collector voltage of 1 V. A  $0.4 \mu\text{m} \times 50 \mu\text{m}$  NMOS transistor, on the other hand, has a typical  $V_T$  and  $I_{ON}$  of, respectively, 0.5 V and 21 mA at a drain voltage of 3.3 V. Measured  $f_T$  for the NMOS is 15 GHz which has been obtained for a drain voltage and current of 3.3 V and 5 mA.

### IV. MICROWAVE PERFORMANCE

On-wafer Cascade Microtech probes were utilized to evaluate microwave performance for developed bipolar and MOS amplifiers, mixers, and converter chips.

#### A. RF Amplifier

Measured small signal gain and noise figure characteristics, as well as input power dependence at a frequency of 2.4 GHz for the RF amplifier are, respectively shown in Figs. 5 and 6. The amplifier draws 5 mA from a 2 V bias supply to exhibit a small signal power gain higher than 15 dB, and a noise figure lower than 4 dB for a frequency of up to 4 GHz. The output power at 1-dB gain compression point is about 0 dBm for an input signal frequency of 2.4 GHz.

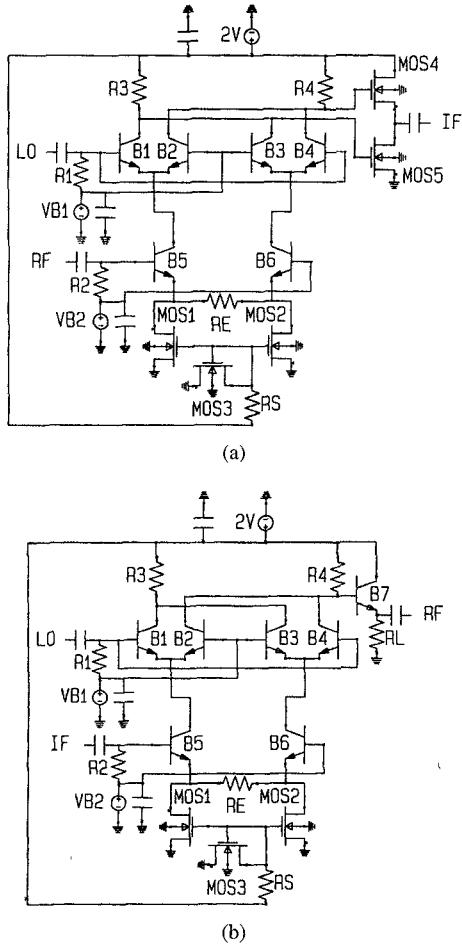

#### B. IF Amplifier

Measured small signal gain and noise figure characteristics, as well as input power dependence at a frequency of 400 MHz for the IF amplifier are, respectively shown in Figs. 7 and 8. The amplifier draws 3 mA from a 2 V bias supply to exhibit a

(a)

(b)

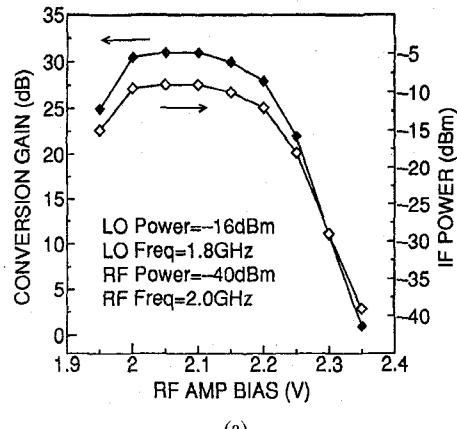

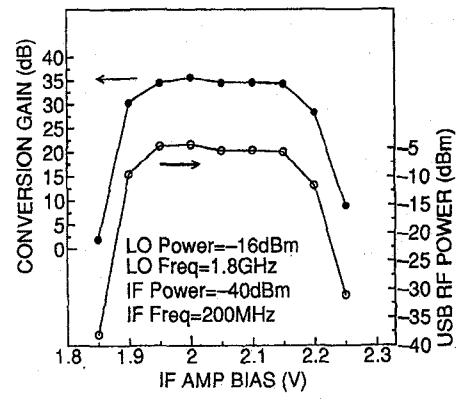

Fig. 14. (a) Downconverter and (b) upconverter performance versus dc bias change.

small signal power gain higher than 13 dB, and a noise figure lower than 2.5 dB for a frequency of up to 1 GHz. The output power at 1-dB gain compression point is about  $-5$  dBm for an input signal frequency of 400 MHz.

#### C. Mixers

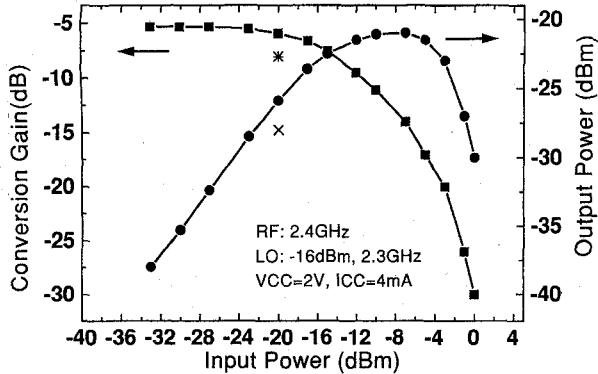

For an LO frequency and power level of 2.3 GHz and  $-16$  dBm and an RF frequency of 2.4 GHz, input power dependence of the conversion gain and output power for the mixers used in the downconverter and upconverter chips were investigated. Results are shown in Fig. 9. Block circles and squares, respectively, represent the conversion gain and output power for the downconverter mixer, while the asterisk and plus signs represent, respectively those for the upconverter mixer. Both mixers exhibit a small signal conversion gain of higher than  $-8$  dB for an input power lower than  $-20$  dBm, under a 2 V bias condition.

#### D. Downconverter and Upconverter

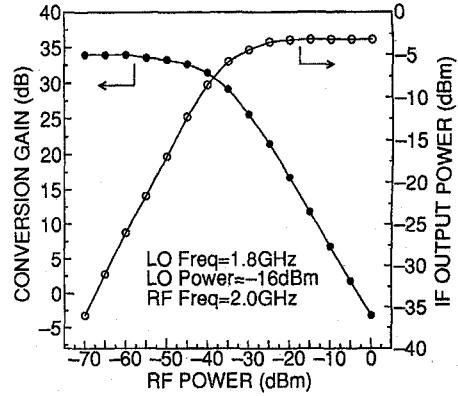

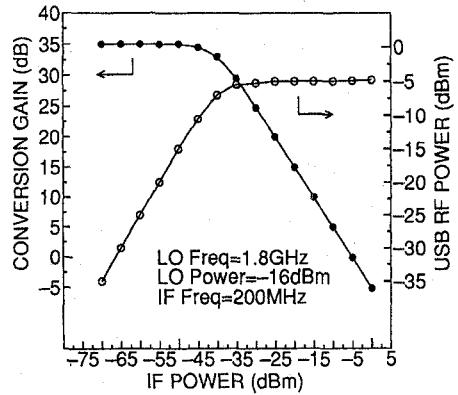

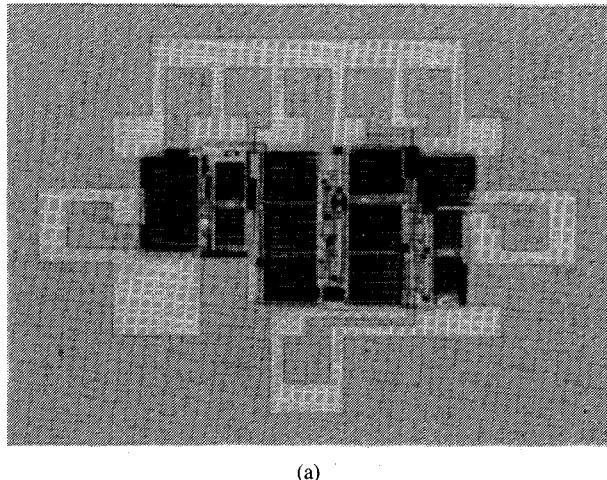

Chip microphotograph for each frequency converter module is shown in Fig. 10. Chip size for both the downconverter and upconverter modules is  $1.0 \text{ mm} \times 0.7 \text{ mm}$ . Fig. 11 depicts conversion gain as well as output power variation versus input power for an LO frequency of 1.8 GHz and an LO power of  $-16$  dBm. The developed modules exhibit an input dynamic range of 40 dB. Maximum conversion gain for the

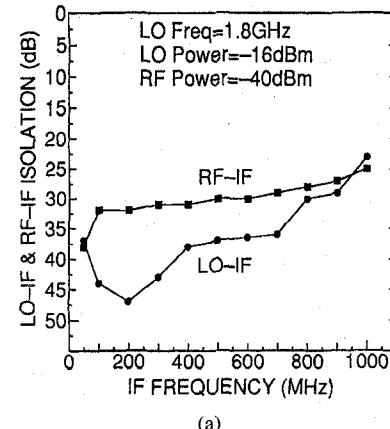

(a)

(b)

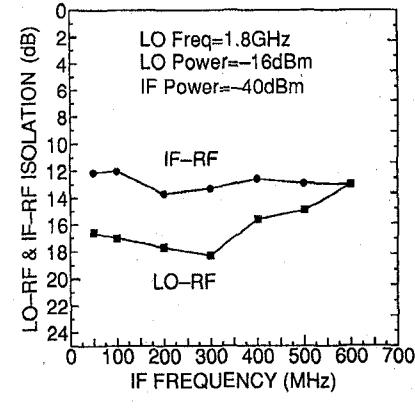

Fig. 15. (a) Downconverter and (b) upconverter port-to-port isolation characteristics.

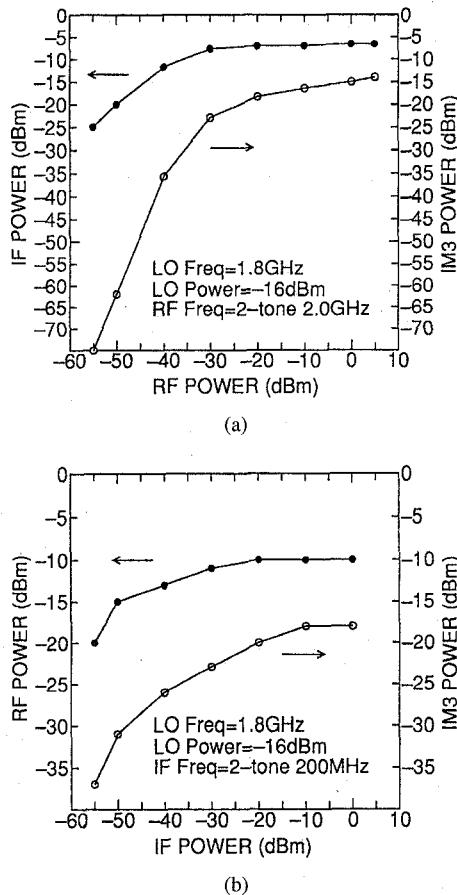

downconverter and the upconverter modules is, respectively, 34 and 35 dB. Fig. 12 represents conversion gain and output power against LO power for an LO frequency of 1.8 GHz and an input power level of  $-40$  dBm. The converters operate with an LO power level as low as  $-40$  dBm, and maximum conversion gain is obtained at an LO power of  $-16$  and  $-10$  dBm, respectively, for the downconverter and upconverter. Performance of the downconverter and upconverter chips versus the IF frequency, for an input power of  $-40$  dBm, an LO power of  $-16$  dBm, and the LO frequency as a parameter, is shown in Fig. 13. Noting that  $RF = LO + IF$ , both chips can cover the 1.8–6.2 GHz band with an IF frequency up to 1000 MHz and sufficient conversion gain. Fig. 14 shows conversion gain and output power versus RF amplifier bias voltage for the downconverter, and IF amplifier bias voltage for the upconverter. While the maximum conversion gain is achieved for a dc voltage of 2.05–2.10 V, both chips exhibit a graceful degradation for a  $\pm 0.15$  V voltage deviation. As shown in Fig. 15, measured LO-IF and RF-IF isolation for the downconverter is better than 30 dB for an IF frequency of up to 500 MHz, and better than 23 dB for an IF frequency of up to 1000 MHz. On the other hand, maximum LO-RF and IF-RF isolation for the upconverter is, respectively, 18 and 14 dB. Third order intermodulation product power levels for the downconverter and upconverter were measured to be 5 dBm, as indicated in Fig. 16. Power dissipation for each frequency converter module is 24 mW.

Fig. 16. (a) Downconverter and (b) upconverter 3rd order intermodulation characteristics.

## V. CONCLUSION

Design considerations and performance results for low-voltage Si MMIC's including RF and IF amplifiers, Gilbert mixers, and downconverter/upconverter chips developed for mobile and personal communications applications were described. By an optimum selection of bipolar and MOS technologies for different parts in each module, a low-power 2 V operation covering the full frequency range of 1.8–5.2 GHz was realized. The developed modules are expected to find applications in 2 V-class PCS/DECT, ISM-band WAN, Hiperlan systems, and also their dual-mode operation.

## ACKNOWLEDGMENT

Thanks are due to K. Maruhashi for his help during noise measurements. The authors are also indebted to M. Nakamae and S. Hasegawa for their support.

## REFERENCES

- [1] J. Loraine, "Wireless data networks: An opportunity for GaAs," in *GaAs IC Symp. Dig.*, Oct. 1993, p. 11.

- [2] P. Weger, W. Simburger, H. Knapp, T. C. Leslie, N. Rohringer, J. Popp, G. Schultes, A. Scholtz, and L. Treitinger, "Completely integrated 1.5 GHz direct conversion transceiver," in *VLSI Circuits Symp. Dig.*, June 1994, p. 135.

- [3] V. Thomas, J. Fenk, and S. Beyer, "A one-chip 2 GHz single superhet receiver for 2 Mbps FSK radio communication," in *IEEE ISSCC Dig.*, Feb. 1994, p. 42.

- [4] J. Sevenhuijsen *et al.*, "An analog radio front-end chip set for a 1.9 GHz mobile radio telephone application," in *IEEE ISSCC Dig.*, Feb. 1994, p. 44.

- [5] T. Tsukahara *et al.*, "A 2 V 2 GHz Si-bipolar direct-conversion quadrature modulator," in *IEEE ISSCC Dig.*, Feb. 1994, p. 40.

- [6] C. Takahashi, R. Fujimoto, S. Arai, T. Itakura, T. Ueno, H. Tsurumi, H. Tanimoto, S. Watanabe, and K. Hirakawa, "A 1.9 GHz Si direct conversion receiver IC for QPSK modulation systems," in *IEEE ISSCC Dig.*, Feb. 1995, p. 138.

- [7] J. R. Long, M. A. Copeland, P. Schvan, and R. A. Hadaway, "A low-voltage silicon bipolar RF front-end for PCN receiver applications 1 ns," in *IEEE ISSCC Dig.*, Feb. 1995, p. 140.

- [8] H. Okamura *et al.*, "A 1 ns, 1 W, 2.5 V, 32 kb NTL-CMOS SRAM macro using a memory cell with P-channel access transistors," in *IEEE ISSCC Dig.*, Feb. 1995, p. 306.

**Mohammad Madhian** (S'81–M'83–SM'88) was born in Tehran, Iran, on January 3, 1954. He received the B.Sc. degree from Iran University of Science and Technology, Tehran, Iran, in 1976, and the M.Sc. and Ph.D. degrees from Shizuoka University, Hamamatsu, Japan, in 1980 and 1983, respectively, all in electronic engineering.

In 1983, he joined NEC Microelectronics Research Laboratories, Kawasaki, Japan, where he has worked on research and development of compound semiconductor device-based digital as well as microwave monolithic IC's. From 1989 to 1991, he was the Chief Technical Advisor to NEC Tehran Office and Iran Telecommunications Industries Company. He is presently a Principal Researcher at NEC C&C Research Laboratories, Kawasaki, where he conducts research and development of GaAs-based monolithic millimeter-wave IC's and BiCMOS-based MMIC's for high speed wireless LAN and personal communications applications.

Dr. Madhian has received the 1988 IEEE Microwave Prize. Since 1994, he has been serving on the IEEE GaAs IC Symposium Technical Program Committee.

**Kiyotaka Imai** received the B.E. and M.E. degrees in electronics engineering from Hokkaido University in 1984 and 1986, respectively.

He joined NEC Corporation in 1986 and is now an Assistant Manager of the Logic Device Development Laboratory, ULSI Device Development Laboratories, Shimokuzawa, Sagamihara. He is engaged in the research and development of BiCMOS devices.

Mr. Imai is a member of the Institute of Electronics, Information, and Communication Engineers.

**Hiroshi Yoshida** received the B.E. and M.E. degrees in electrical engineering from Muroran Institute of Technology in 1985 and 1987, respectively.

He joined NEC Corporation in 1987 and is now an Assistant Manager of the Logic Device Development Laboratory, ULSI Device Development Laboratories, Shimokuzawa, Sagamihara. He is engaged in the research and development of BiCMOS devices.

**Yasushi Kinoshita** received the B.S. degree in applied physics from Science University of Tokyo, Tokoyo, and M.S. in physics from Tsukuba University, Tsukuba, in 1987 and 1989, respectively.

He joined NEC Corporation in 1989 and is now a Member of the Logic Device Development Laboratory, ULSI Device Development Laboratories. He is engaged in the research and development of BiCMOS devices.

Mr. Kinoshita is a member of the Japan Society of Applied physics.

**Tohru Yamazaki** received the B.E. and M.E. degrees in electrical engineering from Seikei University in 1976 and 1978, respectively.

He joined NEC Corporation in 1978 and is now Senior Manager of the Logic Device Development Laboratory, ULSI Device Development Laboratories, Shimokuzawa, Sagamihara. He is engaged in the research and development of BiCMOS devices.